下面的所有内容在Design Compiler User Guide中基本上都有提到,如果需要更加严谨完整的描述,请看文档!

本文档不仅仅是手册的提取和翻译,同时有自己的理解和想法,但是也可能引入错误。

同时本文档参考了IC_learner的博客:https://www.cnblogs.com/IClearner/tag/DC/. 我参考的文档,是他在大三的时候写的,而现在我也正好是大三,还是和别人有一定的差距。

综合的基本流程

- 读入硬件描述语言代码

- 将硬件描述语言根据GTECH库和DesignWare库(如果使用的话),转为与工艺库无关的网表。 GETCH(generic technology):简单的逻辑门,如与或非,触发器; DesignWare:包含了更复杂的逻辑电路,如加法器,比较器等。

- 映射到指定的工艺库

- 进行时序优化门极网表

- 导出文件,可进入下一阶段的布局布线

综合时的优化

DC会有三总层级的优化:

- 结构级优化

- 逻辑级优化

- 门极优化

结构级优化(Architectural Optimization)

结构级优化会共享相同的子表达式,会进行资源共享,会使用DesignWare去实现电路,同时会更改算术表达式达到最好的路径延迟。

共享子表达式示例:

sum1 <= a + b + c;

sum2 <= a + b + d;DC(可能)会自动优化为:

a_b_temp <= a + b;

sum1 <= a_b_tmp + c;

sum2 <= a_b_tmp + d;资源共享示例:

assign sum = sel ? a+b : a+c; //两个加法器DC(可能)会自动优化为:

assign sum = a + (sel ? a : b); //一个加法器逻辑层级的优化(Logic-Level Optimization)

此时的优化是在GTECH网表上进行的。包含两个步骤:

结构调整(Structuring)

这个和结构级优化(Architectural Optimization)中的共享子表达式差不多,这里也是使用的共享子表达式,但是这个是基于GTECH网表进行的优化。

展平(Flattening)

将组合逻辑网络转为两级的SOP(sum-of-products)形式,SOP就是先与后或的格式。在没有大扇出的情况下可以优化延迟。

门级优化(Gate-Level Optimization)

门极优化从GTECH网表开始,并生成与工艺相关的网表。你可以在dc_shell中执行compile或者compile_ultra来进行这个操作。

包含下面的步骤:

映射(Mapping)

这一步将网表与工艺库连接起来。dc_shell中会看到如下的输出:

延迟优化(Delay Optimization)

这一步会调整在映射阶段的延时违例。

设计规则修整(Design Rule Fixing)

这一步就是通过调整单元的尺寸大小或者插入buffer去满足设计要求。调整尺寸大小:如将ANDX1改为ANDX2以增大驱动能力,在驱动下一级时延迟更小;插入Buffer:增大延时,使之满足保持时间(hold time)的要求。

面积优化(Area optimization)

除了上面提到的优化之外,还有Leakage Power, WLM Backend等优化。

上述不同的优化之间会产生冲突,如优化延迟导致面积增大,在DC中可以使用set_cost_prority来设置优先级,对于该命令的使用,可以在dc_shell中用man命令来查看。

实际脚本中的综合流程

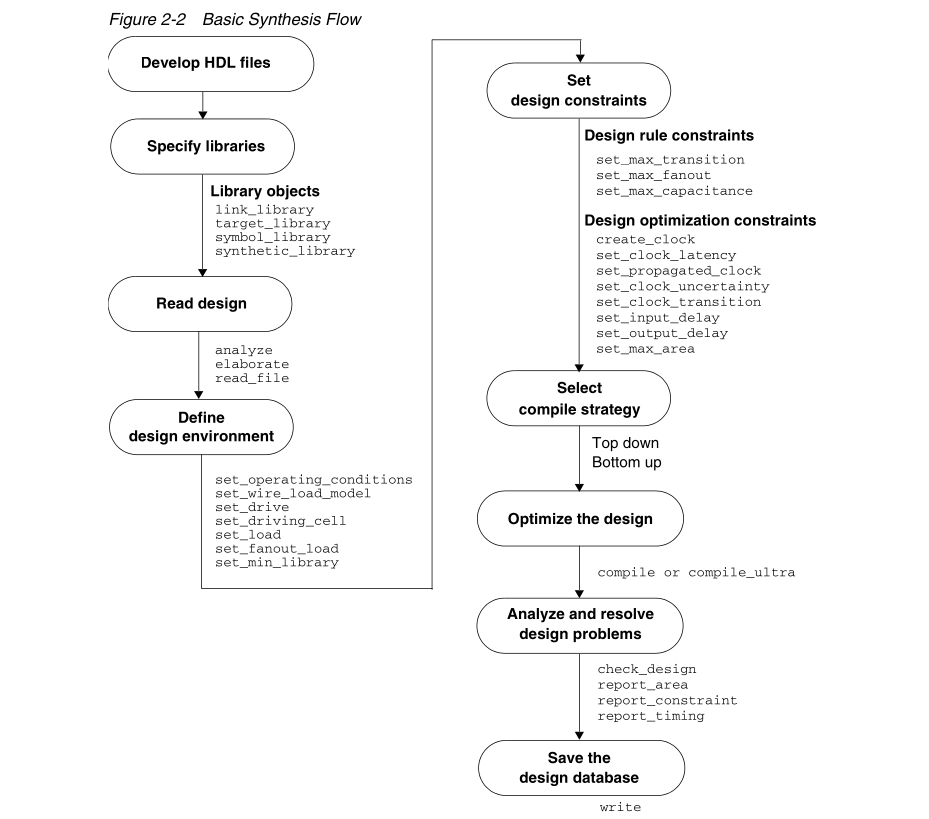

DC手册上下图,很好的表示的综合的脚本流程:

这个图描述的很清楚,我只是想在这里提一下"编译策略(Compile Strategy)":

编译策略分为两种,Top down 和 Bottom up. 自顶向下的策略会读取所有的HDL文件,同时编译所有的设计文件,可用于较小的工程。而自底向下则是将整个设计模块分成若干子模块,然后分别对每个子模块进行编译,最后再编译上层模块,直到整个设计都被编译完成,通常情况下,可以对编译好的子模块设置dont_touch,防止在后续的编译中被修改。

参考:

- Design Compiler User Guide

- IC_learner-博客园(https://www.cnblogs.com/IClearner/tag/DC/)

最新回复